IBIS-Modelle Signalintegrität und Wellenwiderstand von Bauelementen

Im IBIS-Modell finden sich die Angaben zum Wellenwiderstand und zur Kapazität aller Pins – man muss lediglich wissen, wo man nach diesen Angaben zu suchen hat. Dieser Schaltungstipp erläutert die Vorgehensweise.

Beim Versuch, Signale bei der Übertragung auf einer Leiterplatte zu stabilisieren, können Signalintegritäts-Probleme eine Reihe interessanter Effekte hervorrufen. Eine einfache Lösung für diese Probleme bringen die IBIS-Modelle, aus denen sich wichtige Variablen für Signalintegritäts-Berechnungen und das Leiterplattendesign extrahieren lassen.

Die Werte, die man aus einem IBIS-Modell entnehmen kann, sind ein integraler Bestandteil der Berechnungen, die beim Design zum Thema Signalintegrität durchgeführt werden. Beim Anpassen von Leitungen in einem System müssen die elektrischen Impedanzen und Eigenschaften der integrierten Schaltungen und Leiterbahnen bekannt sein.

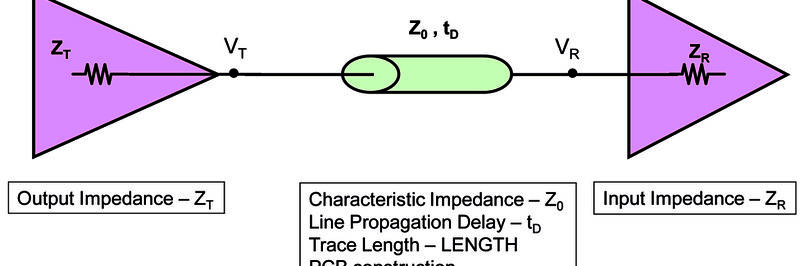

Bild 1: Schema einer massebezogenen Übertragungsleitung mit Sender, Leitung und Empfänger (Bild: TI)

Bild 1: Schema einer massebezogenen Übertragungsleitung mit Sender, Leitung und Empfänger (Bild: TI)Bild 1 zeigt eine Prinzipdarstellung einer massebezogenen Leitung. Für die Leitung können die Ausgangs-Impedanz des Senders (ZT, Ω) und die Eingangsimpedanz des Empfängers (ZR, Ω) aus dem IBIS-Modell des Schaltkreises entnommen werden. Die Datenblätter der IC-Hersteller enthalten diese Angaben unter Umständen nicht, doch lassen sich die Werte allesamt aus dem IBIS-Modell des betreffenden Bausteins extrahieren.

Wellenwiderstand, Signallaufzeit und Leiterbahnlänge

Übertragungsleitungen werden durch vier Parameter definiert: den Wellenwiderstand (Z0, Ω), die spezifische Signallaufzeit auf der Leiterplatte (D, ps/cm), die Signallaufzeit in der Leitung (tD, s) und die Leiterbahnlänge (LENGTH, cm). Der Z0-Wert einer FR-4-Leiterplatte liegt typischerweise zwischen 50 und 75 Ω, während D zwischen 55 und 71 ps/cm beträgt. Die tatsächlichen Werte von Z0 und D hängen vom Werkstoff der Übertragungsleitung und ihren mechanischen Abmessungen ab [1]. Die Signallaufzeit (tD) auf der jeweiligen Leiterplatte ist das Produkt aus der spezifischen Signallaufzeit D und der Leiterbahnlänge LENGTH. Bei FR-4-Platinen mit einem Wellenwiderstand von 50 Ω liegt die spezifische Signallaufzeit einer Leiterbahn bei 70 ps/cm.

Entscheidend ist die Ausgangsimpedanz

Der entscheidende Wert, der zur Beurteilung der Signalintegrität benötigt wird, ist die Ausgangsimpedanz ZT. Damit man die Ausgangsimpedanz ermitteln kann, enthält der mit [Pin] überschriebene Bereich des IBIS-Modells die ohmschen, induktiven und kapazitiven Widerstandskomponenten zu jedem Pin. Um ein klareres Bild zu erhalten, nimmt man zur Gehäusekapazität noch die Kapazität des jeweiligen Puffers (C_comp) hinzu.

Bild 2: Das Listing des Modells ads1296zxg samt der Werte für C_pin (Bild: TI)

Bild 2: Das Listing des Modells ads1296zxg samt der Werte für C_pin (Bild: TI)Das Schlüsselwort [Pin] bezieht sich auf ein bestimmtes Gehäuse, das von den Angaben unter [Component], [Manufacturer] und [Package] oberhalb des Schlüsselworts [Pin] beschrieben wird. Man findet die Gehäuse spezifische Kapazität und Induktivität für den jeweiligen Pin in der Tabelle zum Schlüsselwort [Pin]. Zum Beispiel ist im Modell ads129x.ibs [2] (Bild 2) zu sehen, wo man nach den Werten L_pin und C_pin des Signals GPIO4 an Pin 5E (PBGA-64-Gehäuse) suchen muss. Die Werte L_pin (Pin-Induktivität) und C_pin (Pin-Kapazität) für dieses Signal und dieses Gehäuse lauten 1,489 nH bzw. 0,28001 pF. Der zweite interessierende Kapazitätswert ist die Angabe C_comp unter dem Schlüsselwort [Model]. Bild 3 zeigt ein Beispiel für die Auflistung von C_comp im Modell DIO_33 [2].

![Bild 3: Beispiel für die Auflistung von C_comp im Modell DIO_33 [2] (Bild: TI)](https://autor.vogel.de/wp-content/uploads/2013/11/listing2.jpg) Bild 3: Beispiel für die Auflistung von C_comp im Modell DIO_33 [2] (Bild: TI)In Bild 3 steht das Zeichen ‚

Bild 3: Beispiel für die Auflistung von C_comp im Modell DIO_33 [2] (Bild: TI)In Bild 3 steht das Zeichen ‚

Literatur

[1] Johnson, G.: High-speed Digital Design: A Handbook of Black Magic, Prentice Hall, ISBN: 0-13-395724-1 [2] ads129x.ibs, IBIS Model, sbam021b,Texas Instruments [3] Baker, B.: “Beyond the Data Sheet with IBIS”, EDN, 25. Mai 2011

Von Bonnie Baker, Texas Instruments.

:quality(80)/p7i.vogel.de/wcms/c8/1e/c81efe8237fc680c7c14d23751a2c5ee/0127863835v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7a/6a/7a6af3717955b269cf655b9fda07890b/0118745025v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/f8/b6f824e303b426aee0ffc6335f707997/0119443352v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2c/58/2c5810b14b65b16e516364ea089c788a/0118708239v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7f/c5/7fc584ed445088b6472b57cf8ce223f9/0128106511v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3b/ec/3beceace0302f6220cc507da1921a3dd/0127866486v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/31/be312f856882c5c2cf4c71c0bf86bacc/0127866503v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/18/1d1807aec6b9e7153e108d66f5dd2aff/0127093609v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/56/f0/56f0dee1fa1d5a0045c4258b40bd1193/0126767105v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/71/d6/71d6f4aa2d0e4112ab718df71c5ccfb1/0125010024v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fd/75/fd754b0998f6e30d975c8a441c34eb03/0124489399v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e0/96/e096cd446f05afbaa0ad6ded16715528/0112587312.jpeg)

:quality(80)/p7i.vogel.de/wcms/aa/9f/aa9f478067633d609deb87ca1c14467e/69238554.jpeg)

:quality(80)/images.vogel.de/vogelonline/bdb/1690700/1690795/original.jpg)

:quality(80)/p7i.vogel.de/wcms/64/45/64452e8f6684f8c2fb5b4c28978c18e5/0123247120v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/2b/132b287c3a48412cb8cbc6a058309254/94255924.jpeg)

:quality(80)/images.vogel.de/vogelonline/bdb/1745700/1745790/original.jpg)

:quality(80)/p7i.vogel.de/wcms/76/52/76524f60d1ceceec257c91be898abec4/87998596.jpeg)

:quality(80)/p7i.vogel.de/wcms/5c/bb/5cbbd9e4df4baa5929886613b19e35bd/0126651291v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5c/e4/5ce41ec6c6dc30a9f017266e71d9ade6/0125425439v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7f/c5/7fc584ed445088b6472b57cf8ce223f9/0128106511v2.jpeg)