Schaltung PIN-Dioden-Treiber für schnelle Schaltflanken und bipolare Ausgangsspannungen

PIN-Dioden weisen nur geringe Serienverluste und Verzerrungen auf und verkraften hohe HF-Leistungen, die sich mit relativ geringen Steuerspannungen schalten lassen.

PIN-Dioden (p-, n- oder Eigenhalbleiter) werden als Schalter, Dämpfungsglieder und Phasenschieber in HF- und Mikrowellen-Anwendungen eingesetzt. Sie weisen nur geringe Serienverluste und Verzerrungen auf und verkraften hohe HF-Leistungen, die sich mit relativ geringen Steuerspannungen schalten lassen.

PIN-Dioden-Treiber haben die folgenden typischen Eigenschaften: TTL-, CMOS- oder andere Logik-Schnittstellen, bipolare Ausgangsspannung (±3 V für dieses Design) und sie nehmen Ströme von 10 bis 25 mA dauerhaft auf oder treiben diese. Darüber hinaus liefern PIN-Dioden-Treiber Spitzenströme mit kurzen Anstiegs- und Abfallzeiten und verursachen nur minimale Verzögerungen.

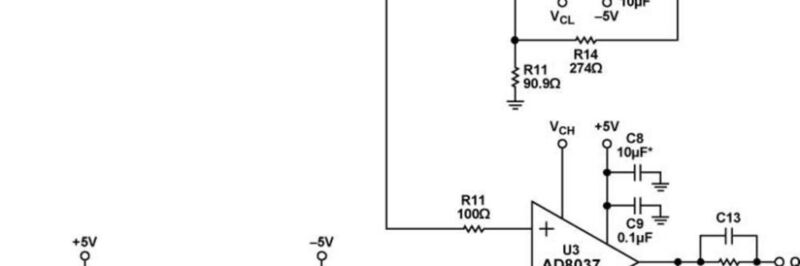

Die Schaltung in Bild 1 erfüllt alle genannten Anforderungen. Als Kernstück dienen zwei Clamp-Verstärker (U2 und U3) des Typs AD8037, die auf eine nicht-invertierende Verstärkung von +4 eingestellt sind. Aufgrund seines speziellen Eingangs-Clamp-Verhaltens ermöglicht der AD8037 ein extrem sauberes und genaues Clamping. Die beiden Verstärker verstärken das Eingangssignal linear bis zu dem Punkt, an dem das Produkt aus Verstärkung und Clamp-Spannungen (Uch und Ucl) überschritten wird.

Bei einer Verstärkung von +4 und Clamp-Spannungen von ±0,75 V ergibt sich eine max. Ausgangsspannung von ±3 V. In diesem Fall ist die Ausgangsspannung viermal höher als die Eingangsspannung, wenn am Eingang weniger als ±0,75 V anliegen. Bei Eingangsspannungen über ±0,75 V wird die Ausgangsspannung auf ±3 V „geklemmt“. Diese Clamping-Eigenschaft ermöglicht beim Übersteuern eine sehr schnelle Erholung (normalerweise weniger als 2 ns). Die Clamp-Spannungen Uch und Ucl erhält man über die Spannungsteiler R2, R3, R7 und R8.

Das XOR-Logik-Gate 74F36 (U1) liefert ein komplementäres Treibersignal für die beiden Verstärker AD8037 (U2 und U3) mit minimalem zeitlichen Versatz zwischen den beiden komplementären Ausgängen. Die Widerstände R4, R5, R9 und R10 sind für die Pegelanpassung des TTL-Ausgangs auf etwa ±1,2 V zuständig. Mit dieser Spannung werden U2 und U3 über R10 und R12 angesteuert.

Bei der hier vorgestellten Schaltung werden die Eingänge von U2 und U3 absichtlich übersteuert, damit die Ausgänge in den „geklemmten“ Zustand gelangen. Somit wird der Ausgangspegel für den PIN-Dioden-Treiber auf ±3 V eingestellt. Die Widerstände R16 und R17 begrenzen den Betriebsstrom. Über die Kondensatoren C12 und C13 wird der Spitzenstrom für die PIN-Dioden eingestellt.

Die abgebildete Schaltung arbeitet mit bis zu 10 MHz, erreicht ein ausgezeichnetes Schaltverhalten und weist eine Gesamtverzögerung von 15 ns auf. Durch Ändern der Verstärkung oder der Clamp-Spannungen können Ausgangsspannung und Strom auf die jeweilige Anwendung optimiert werden.

Der Autor: John Ardizzoni arbeitet bei Analog Devices.

:quality(80)/p7i.vogel.de/wcms/c8/1e/c81efe8237fc680c7c14d23751a2c5ee/0127863835v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7a/6a/7a6af3717955b269cf655b9fda07890b/0118745025v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b6/f8/b6f824e303b426aee0ffc6335f707997/0119443352v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/2c/58/2c5810b14b65b16e516364ea089c788a/0118708239v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7f/c5/7fc584ed445088b6472b57cf8ce223f9/0128106511v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/3b/ec/3beceace0302f6220cc507da1921a3dd/0127866486v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/31/be312f856882c5c2cf4c71c0bf86bacc/0127866503v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/18/1d1807aec6b9e7153e108d66f5dd2aff/0127093609v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/56/f0/56f0dee1fa1d5a0045c4258b40bd1193/0126767105v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/71/d6/71d6f4aa2d0e4112ab718df71c5ccfb1/0125010024v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fd/75/fd754b0998f6e30d975c8a441c34eb03/0124489399v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e0/96/e096cd446f05afbaa0ad6ded16715528/0112587312.jpeg)

:quality(80)/p7i.vogel.de/wcms/aa/9f/aa9f478067633d609deb87ca1c14467e/69238554.jpeg)

:quality(80)/images.vogel.de/vogelonline/bdb/1690700/1690795/original.jpg)

:quality(80)/p7i.vogel.de/wcms/64/45/64452e8f6684f8c2fb5b4c28978c18e5/0123247120v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/13/2b/132b287c3a48412cb8cbc6a058309254/94255924.jpeg)

:quality(80)/images.vogel.de/vogelonline/bdb/1745700/1745790/original.jpg)

:quality(80)/p7i.vogel.de/wcms/76/52/76524f60d1ceceec257c91be898abec4/87998596.jpeg)

:quality(80)/p7i.vogel.de/wcms/5c/bb/5cbbd9e4df4baa5929886613b19e35bd/0126651291v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/c1/04c1b4e6b06680d2030f3f7520531368/0125479713v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/23/2a/232a9b21b32d54b92676e87cdb0ee13a/0125052285v2.jpeg)